Le projet en détail

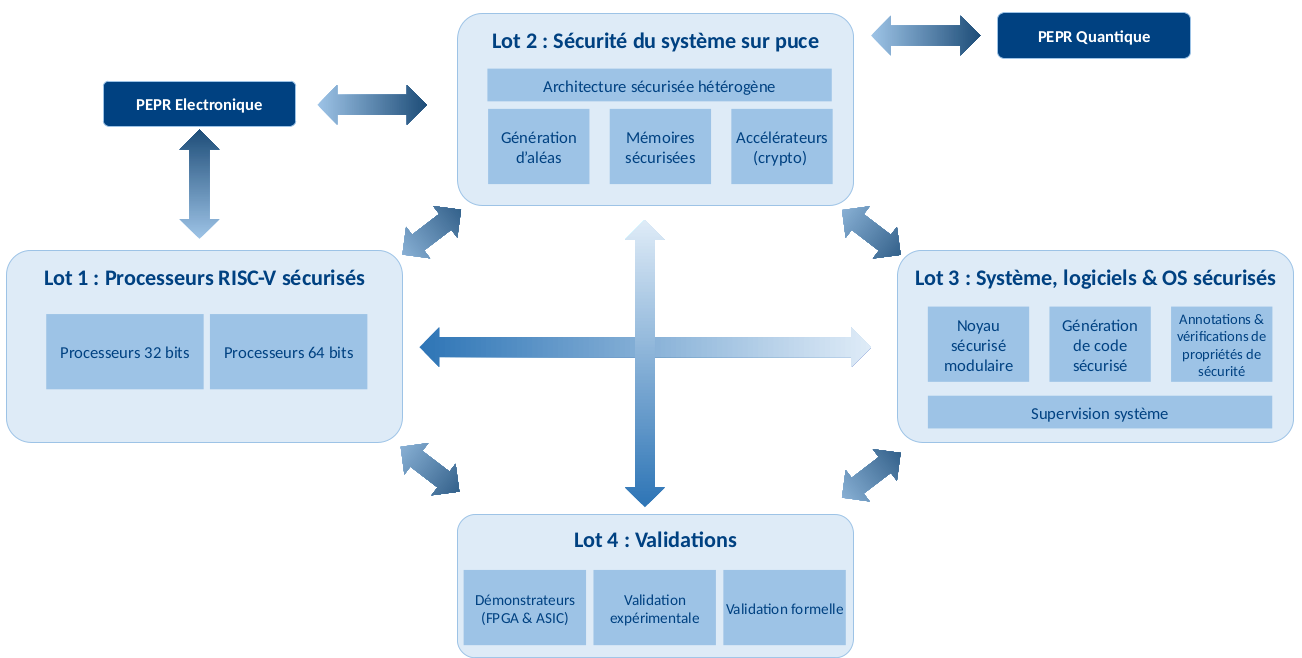

Le projet ARSENE vise à développer un ensemble de briques matérielles, logicielles et d’outils pour constituer une offre française de “System on Chip” (SoC) sécurisé. Le projet est structuré en 4 lots principaux :

- Lot 1 - RISC-V sécurisé : Sécurisation de deux familles de processeurs RISC-V, pour les rendre robustes l’une (32-bit) aux attaques physiques et l’autre (64-bit) aux attaques microarchitecturales.

- Lot 2 - Sécurité du SoC : Étude d’une architecture sécurisée de SoC hétérogène, incluant des accélérateurs cryptographiques, des générateurs de nombres aléatoires et des mémoires sécurisées.

- Lot 3 - Système, logiciels & OS sécurisés : Développement de briques logicielles/matérielles pour exécuter du code sécurisé, avec des objectifs tels que la définition des propriétés de sécurité attendues, des annotations au niveau du compilateur et la mise en œuvre d’un noyau OS embarqué.

- Lot 4 - Méthodes et outils de validation : Validation formelle, prototypage FPGA et démonstration ASIC des composants développés dans les lots 1 à 3.

Le projet ARSENE sera étroitement lié aux autres PEPR, en particulier le PEPR Quantique, le PEPR Électronique et le PEPR Cybersécurité, pour assurer une approche cohérente et collaborative.